MOSFETs und Einführung CMOS Logikgatter - Abkürzungen

←

→

Transkription von Seiteninhalten

Wenn Ihr Browser die Seite nicht korrekt rendert, bitte, lesen Sie den Inhalt der Seite unten

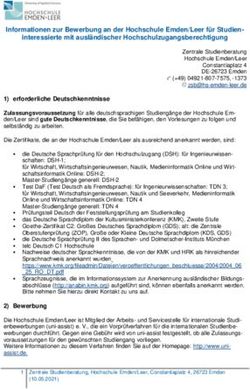

4. MOSFETs und Einführung CMOS‐Logikgatter Abkürzungen: MOSFET = metal‐oxide‐semiconductor field‐effect transistor (deutsch: Metall‐Oxid‐Halbleiter‐Feldeffekttransistor) im folgenden oft als MOS‐Transistor bezeichnet CMOS: Complementary MOS (komplementäre MOS‐Transistoren – also N‐ und P‐Kanal‐MOSFETs auf gemeinsamen Substrat) Inhalt: MOSFETs: Funktionsweise und elektrisches Verhalten Komplementäre Gatter in Schalterlogik / mit MOSFETs Elektrische Charakteristiken von CMOS‐Gattern (statisch + dynamisch + erste Modellbildung) Auswirkungen von Transistorverkleinerungen (Shrinking) 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 103 103

Herkunft Folien Viele Folien zu dieser Vorlesung stammen aus der Vorlesung „Technische Informatik“ und „Entwurf Integrierter Schaltungen“ von Prof. Dr. Wolfgang Nebel Universität Oldenburg, Department Informatik Für die Genehmigung der Verwendung möchte ich mich hier besonders bedanken! Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 104 104

Physikalischer Aufbau des N‐Kanal MOS‐Transistors x=0 x=L x Poly SiO2 W Gate "G" n p n d Drain "D" Kanal Source "S" Si Substrat "B" G D S Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 105 Das am häufigsten verwendete Halbleitermaterial zur Fertigung von N‐Kanal MOS‐Transistoren (kurz NMOS‐Transistoren) ist Silizium. Die oben dargestellte Struktur besteht aus einem schwach p‐dotiertem Substrat. Über dem N‐Kanal befindet sich eine Isolationsschicht (Silizium‐Dioxid – SiO2) der Dicke d – auch Dünnoxid genannt. Auf der Isolationsschicht wird im Herstellungsprozess leitfähiges Polysilizium (Poly) aufgewachsen, das den Gate‐Anschluss des Transistors bildet. Die Ausmaße des Gates begrenzen gleichzeitig die Länge und die Weite des Kanals (L=Länge, W=Weite). Im p‐Substrat werden an den Grenzen zum Kanal‐Bereich die n‐ dotierten Source‐ und Drain‐Gebiete eindiffundiert. Dadurch ergibt sich nun der N‐Kanal MOS‐ Transistor mit der Kanallänge L, der Weite W und der Dicke der Isolationsschicht d. Durch Anlegen einer Gate‐Source‐Spannung, die größer als die im Herstellungsprozess eingestellte Schwellwertspannung (Threshold‐Spannung) ist (UGS>UTH), bildet sich im P‐Substrat ein N‐ leitender Kanal (die Minoritätsladungsträger der Elektronen werden im P‐Substrat in Richtung Gate gezogen und bilden dadurch den Kanal). Unten ist das gebräuchliche Schaltsymbol dargestellt. Je nach Dotierung des Transistors im Kanalbereich (unter der SiO2‐Isolation) kann man selbstleitende (UTH0V) herstellen. Im Kontext der CMOS‐ Technologie werden nur selbstsperrende Transistoren verwendet. Durch die Isolationsschicht ist das Gate von den restlichen Anschlüssen des Transistors galvanisch getrennt und das Gate bildet entsprechend einen Kondensator mit dem Kanal. Entsprechend wird über die Gate‐Source‐Spannung (UGS) der Kanal und damit der Kanalwiderstand gesteuert. Im Gegensatz zum Bipolar‐Transistor erfolgt die Steuerung also über eine Spannung und nicht über einen Strom (Basis‐Strom beim Bipolar‐Transistor). Entsprechend erfolgt die statische Ansteuerung eines MOS‐Transistors verlustleistungsfrei – beim Schalten muss natürlich die Gate‐Kapazität umgeladen werden. 105

n‐Kanal MOS‐Transistor Drain iD im stabilen Zustand: iG=0 uDS iG iD=iS=iDS uGS iS Source Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 106 Wie auf der vorherigen Folie bereits beschrieben, bildet das Gate mit dem Kanal und der dazwischen liegenden Isolationsschicht einen Kondensator. Damit gelten für das Verhalten des Gates auch die bekannten Kondensator‐Charakteristiken. Im stabilen Zustand fließt durch den Gate‐Anschluss entsprechend kein Strom. Beim An‐ und Abschalten des Transistors ist dies natürlich anders, da der Gate‐Kondensator umgeladen werden muss. Über die Gate‐Source Spannung UGS wird der „Kanalwiderstand“ gesteuert. Ähnlich wie beim Bipolar‐Transistor wird die Beziehung zwischen IDS und UDS durch ein Kennlinienfeld beschrieben – und nicht durch eine einfache lineare Funktion wie beim Widerstand. Dieses Kennlinienfeld ist auf der nächsten Folie dargestellt. Das Source‐Potential ist in der Praxis kleiner oder gleich den Potentialen der 3 Anschlüsse Drain, Gate und Source. Bezüglich der physikalischen Bauform unterscheiden sich Drain und Source nicht – anders als beim Bipolar‐Transistor. Die Unterscheidung erfolgt entsprechend nur durch die Verschaltung: an Source liegt das niedrigere Potential. Damit kann man die Anschlüsse auch vertauschen. Zu beachten ist aber, dass der Bulk‐Anschluss (Substrat‐Anschluss) oft mit dem Source‐Anschluss verbunden wird (und keinesfalls mit dem Drain‐Anschluss). 106

Kennlinie des n‐Kanal MOS Transistors iDS uDS=uGS‐UTH linearer Bereich Sättigung uGS Sperrbereich: uGS < UTH; iDS = 0 uDS Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 107 Für den Sperrbereich (UGS

P‐Kanal MOS‐Transistor Source iS im stabilen Zustand: uGS iG=0 uDS iS=iD= ‐iDS Gate iG uGS ≤ 0V iD Drain uDS ≤ 0V Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 108 Der physikalische Aufbau des p‐Kanal‐MOS‐Transistors ist bezüglich der Struktur mit dem des n‐ Kanal‐MOS‐Transistors vergleichbar (siehe Folie „Physikalischer Aufbau des N‐Kanal MOS‐ Transistors “). Als Substrat wird schwach n‐dotiertes Silizium verwendet. Source und Drain bestehen aus p‐dotierten Diffusionsgebieten. Da die Leitfähigkeit von Löchern ca. um den Faktor 2 unter denen der Elektronen liegt, müssen P‐Kanal MOS‐Transistoren um den Faktor 2 weiter ausgelegt werden (siehe W in Folie „Physikalischer Aufbau des N‐Kanal MOS‐Transistors “). Um einen p‐Kanal unter der Isolationsschicht zu bilden, muss am Gate eine negative Spannung gegenüber dem Source‐Anschluss angelegt werden (Löcher werden in Richtung Isolationsschicht gezogen und bilden damit den Kanal). In der Praxis liegt damit das Source‐Potential beim N‐ Kanal‐MOS‐Transistor auf dem niedrigsten Potential der 3 Anschlüsse Gate, Source und Drain. Beim P‐Kanal‐MOS‐Transistor liegt das Source‐Potential auf dem höchsten Potential der 3 Anschlüsse Gate, Source und Drain. Der Transistor sperrt wenn UGS>UTH (mit UTH

Kennlinie des P‐Kanal MOS‐Transistors i DS Sperrbereich: UGS > UTH; iDS = 0 uDS Sättigung uGS linearer Bereich uDS=uGS‐UTH Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 109 Hier ist das Kennlinienfeld eines P‐Kanal‐MOSFETs analog zum Kennlinienfeld eines N‐Kanal MOS‐FETs dargestellt. Wie bereits erklärt, schaltet der Transistor durch, wenn UGS > UTH – je kleiner UGS ist, umso „besser“ leitet der Transistor. (Achtung: wir sprechen von negativen Spannungen, die wenn sie kleiner werden betragsmäßig größer werden…). iDS fließt wird vom Drain zum Source positiv gezählt und er ist hier entsprechend immer negativ. Das prinzipielle Verhalten ist ansonsten analog von den Kennlinien der N‐Kanal‐MOSFETs übertragbar (Sättigung, …). 109

Gatter in Schalterlogik ‐ Idealer Schalter Ein idealer Schalter unterbricht im Zustand „offen“ einen Stromkreis, so dass i = 0, unabhängig von u. i u Er schließt im Zustand „geschlossen“ den Stromkreis, so dass u = 0, unabhängig von i. i i geschlossen offen u u Kennlinie des idealen Schalters Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 110 110

Reale Schalter Reale Schalter haben sowohl einen (kleinen) Widerstand im Zustand „geschlossen“, als auch einen (großen) Widerstand im Zustand „offen“. i u > 0 auch im geschlossenen R1 R1 0 auch im geöffneten In der Praxis kann R2 oft ver‐ Zustand i nachlässigt werden (R2 ) Kennlinie geschlossen des realen offen Schalters u Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 111 111

Schalter nicht invertierender invertierender Schalter Schalter A C 0 offen geschlossen 1 geschlossen offen A B Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 112 112

Struktur von CMOS‐Schaltungen UDD Regeln: pull‐up und pull‐down Blöcke schaltet pull‐ auf „1“ dürfen nicht gleichzeitig leiten up Kurzschluss Block d.h.: pull‐up und pull‐down Ein‐ Ausgang Blöcke sind Komplementär gänge (entweder der eine oder der pull‐ andere Block schaltet durch) down schaltet Block auf „0“ USS Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 113 Anmerkung zu den Potential/Spannungs‐Bezeichnern: UDD/USS: Bezeichner, die für MOS‐Schaltungen gebräuchlich sind – UDD bezeichnet das Versorgungsspannungspotential und USS das Massepotential. UCC/Gnd: entsprechende Bezeichner, die für Schaltungen mit Bipolar‐Transistoren gebräuchlich sind. 113

NAND‐Gatter aus Schaltern A 0 offen geschlossen A B 1 geschlossen offen UDD X iX A B UX X uX 0 0 UDD 1 0 1 UDD 1 1 0 UDD 1 1 1 0 0 Spielen Sie die 4 Kombinationen von A, B durch. Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 114 114

Transistor als Schalter C Source Source Gate Gate p‐Kanal A Drain Drain B oder C Drain Drain Gate Gate n‐Kanal A Source Source B Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 115 Bei den rechten beiden Symbolen wird der Bulk (Substrat) Kontakt durch den Pfeil symbolisiert. In diesem Skript werden primär folgende Symbole verwendet: P‐Kanal‐Transistor: Bulk und Source liegen auf selbem unterschiedlichem Potential N‐Kanal‐Transistor: Bulk und Source liegen auf selbem unterschiedlichem Potential Das Substrat liegt bei P‐Kanal‐Transistoren typischerweise auf UDD und bei N‐Kanal‐Transistoren auf USS‐Potential. 115

CMOS NAND nach WeEs85 A B UDD X iX A B UX X/out 0 0 UDD 1 0 1 UDD 1 1 0 UDD 1 Spielen Sie die 4 Kombinationen von A, B durch 1 1 0 0 (0 ↔ U ; 1 ↔ U ). Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 116 116

Struktur von CMOS‐Schaltungen UDD Regeln: pull‐up und pull‐down Blöcke schaltet pull‐ auf „1“ dürfen nicht gleichzeitig leiten up Kurzschluss Block d.h.: pull‐up und pull‐down Ein‐ Ausgang sind Komplementär gänge Realisierung (MOSFETs): pull‐ pull‐up Blöcke bestehen aus down p‐Kanal‐Transistoren, die bei schaltet Block „0“ am Gate gut leiten auf „0“ pull‐down Blöcke bestehen USS aus n‐Kanal‐Transistoren, die bei „1“ am Gate gut leiten Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 117 Anmerkung zu den Potential/Spannungs‐Bezeichnern: UDD/USS: Bezeichner, die für MOS‐Schaltungen gebräuchlich sind – UDD bezeichnet das Versorgungsspannungspotential und USS das Massepotential. UCC/Gnd: entsprechende Bezeichner, die für Schaltungen mit Bipolar‐Transistoren gebräuchlich sind. 117

Warum keine N‐Kanal‐MOSFETs im Pullup‐Netzwerk? Gedankenexperiment: t = 0: C ist entladen, uout = 0V, uG = 0V t > 0: uG wird sehr langsam erhöht bis uG = UDD (t ≥ te) t = t0: uG = Uth, uGS Uth t = te: uG = UDD, uGS = ? uGS=UG‐uout U G D UDD uGS=UG‐uout=Uth UDD uGS S uG uout uG uout C Uth uGS=UG‐uout uGS=UG‐uout uout t0 te t Kann der n‐Kanal‐Transistor ein Signal auf eine „saubere“ logische „1“ ziehen? Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 118 Die hier dargestellte Schaltung kann als Ausschnitt aus einer CMOS‐Schaltung interpretiert werden: • der N‐Kanal MOSFET wird als Pullup‐Transistor verwendet (Pullup‐Netzwerk), • Der Kondensator zwischen dem Ausgang und Masse repräsentiert die Summe aller am Ausgang angeschlossenen Gate‐Kapazitäten und Verdrahtungskapazitäten (jede Leitung hat auch eine kapazitive Wirkung zum Substrat der integrierten Schaltung und zu anderen Leitungen). Durch das Anschalten des Transistors ist die eigentliche Intention, die Ausgangsspannung uout auf UDD zu erhöhen und den Kondensator komplett aufzuladen. Ob dies gelingt, sollen Sie durch dieses Gedankenexperiment analysieren. Anmerkung: Bei dieser Analyse spielt die Aufladezeit des Kondensators keine Rolle (Exponentialfunktionen), da die zeitliche Änderung von uG so langsam ist, dass die zeitliche exponentielle Änderung in dem hier verwendeten zeitlichen Maßstab nicht erkennbar sein wird. Dadurch, dass der N‐Kanal‐Transistor nur durchschaltet wenn uGS≥UTH ist, muss zunächst geklärt werden, ob der obere Transistor‐Anschluss in der Schaltung Drain oder Source ist. Da der obere Anschluss auf Versorgungsspannungspotential liegt – und dies das höchste (statische) Potential in der Schaltung ist – ist dies der Drain‐Anschluss. Der untere Anschluss ist entsprechend der Source‐Anschluss (die Anschlüsse sind in der Abbildung schon mit D und S beschriftet). Damit liegt der Source‐Anschluss auf einem veränderlichen Potential !!! In der Aufgabenstellung ist nun die Gate‐Spannung (Gate gegenüber Masse) als Eingangssignal gegeben. Der Kondensator ist initial entladen (t = 0: C ist entladen, uout = 0V). Erst wenn der Transistor leitet, kann sich die Ausgangsspannung ändern. Solange der Kondensator also nicht geladen wird (bis t=t0), ist uGS=uG‐ uout=ug (siehe Zeitdiagramm: uGS(blau), uout(rot)). Zum Zeitpunkt t=t0 erreicht damit uGS=Ug die Schwellwertspannung UTH und der Transistor fängt an zu leiten, der Kondensator wird ein wenig aufgeladen und damit steigt minimal uout an, wodurch uGS=UG‐uout sofort wieder unter die Schwellwertspannung fällt und der Transistor wieder sperrt. Entsprechend kann sich zum Zeitpunkt t=t0 die Ausgangsspannung nur minimal (=infinitesimal ‐ in der Abbildung kaum erkennbar) ändern, da durch die Änderung der Transistor sofort wieder sperrt. Nun sollen Sie eigenständig die Spannungsverläufe für t>t0 von uGS(blau) und uout(rot) ergänzen. Anmerkung Folie: Eine logische „0“ wird als „sauber“ bezeichnet, wenn das Signal auf Massepotential liegt. Eine logische „1“ wird als „sauber“ bezeichnet, wenn das Signal auf Versorgungspotential (UDD) liegt. 118

N‐Kanal‐MOSFETs im Pulldown‐Netzwerk Gedankenexperiment: t = 0: C ist auf UDD aufgeladen, uout = UDD, uG = uGS = 0V t > 0: uGS wird sehr langsam erhöht bis uGS = UDD t = t0: uGS = Uth, Transistor „fängt an zu leiten“ t = te: uGS > Uth, Transistor ?leitet? U UDD D uout C uout uG uG=uGS S Uth uGS t0 te t Kann der n‐Kanal‐Transistor ein Signal auf eine „saubere“ logische „0“ ziehen? Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 119 Auch die hier dargestellte Schaltung kann als Ausschnitt aus einer CMOS‐Schaltung interpretiert werden: • der N‐Kanal MOSFET wird als Pulldown‐Transistor verwendet (Pulldown‐Netzwerk), • Der Kondensator zwischen dem Ausgang und Masse repräsentiert die Summe aller am Ausgang angeschlossenen Gate‐Kapazitäten und Verdrahtungskapazitäten (jede Leitung hat auch eine kapazitive Wirkung zum Substrat der integrierten Schaltung und zu anderen Leitungen). Durch das Anschalten des Transistors ist die eigentliche Intention, die Ausgangsspannung uout auf USS (Masse) herunter zu ziehen und den Kondensator komplett zu entladen. Ob dies gelingt, sollen Sie durch dieses Gedankenexperiment analysieren. Anmerkung: Bei dieser Analyse spielt die Aufladezeit des Kondensators keine Rolle (Exponentialfunktionen), da die zeitliche Änderung von uG so langsam ist, dass die zeitliche exponentielle Änderung in dem hier verwendeten zeitlichen Maßstab nicht erkennbar sein wird. Dadurch, dass der N‐Kanal‐Transistor nur durchschaltet wenn uGS≥UTH ist, muss zunächst geklärt werden, ob der untere Transistor‐Anschluss in der Schaltung Drain oder Source ist. Da der untere Anschluss auf Massepotential liegt – und dies das niedrigste (statische) Potential in der Schaltung ist – ist dies der Source‐Anschluss. Der obere Anschluss ist entsprechend der Drain‐Anschluss (die Anschlüsse sind in der Abbildung schon mit D und S beschriftet). Damit liegt der Source‐Anschluss auf dem festen Masse‐ Potential !!! In diesem Fall ist uGS = Ug und damit ist uGS nicht selbst abhängig von uout (vergleiche vorherige Folie). In der Aufgabenstellung ist nun die Gate‐Spannung als Eingangssignal gegeben. Der Kondensator ist initial aufgeladen (t = 0: C ist geladen, uout = UDD). Erst wenn der Transistor leitet, kann sich die Ausgangsspannung ändern – im Zeitintervall [0;t0) liegt die Gate‐Source‐Spannung uGS unterhalb der Schwellwertspannung UTH und damit sperrt der Transistor in diesem Zeitintervall. Der zeitliche Verlauf von uGS(blau) und uout(rot) sind im Zeitintervall [0;t0) bereits dargestellt und sollen von Ihnen für t>t0 nun ergänzt werden. Fassen Sie Ihre Erkenntnisse über das „Durchschalten“ einer logischen „0“ und einer logischen „1“ durch einen N‐Kanal MOSFET abschließend zusammen. Anmerkung Folie: Eine logische „0“ wird als „sauber“ bezeichnet, wenn das Signal auf Massepotential liegt. Eine logische „1“ wird als „sauber“ bezeichnet, wenn das Signal auf Versorgungspotential (UDD) liegt. 119

P‐Kanal‐MOSFETs im Pullup‐Netzwerk Gedankenexperiment: t = 0: C ist entladen, uout = 0V, uGS = 0V, uG = UDD t > 0: uG wird langsam erhöht => uG < UDD, uGS < 0V t = t0: uGS = Uthp, Transistor leitet t = tC: uGS < Uth, Transistor ?leitet? uGS = uG ‐ UDD U UDD uGS S UDD + Uthp uG UDD D uout uG uGS t0 te t C uout Uthp ‐UDD Kann der p‐Kanal‐Transistor ein Signal auf eine „saubere“ logische „1“ ziehen? Kann der p‐Kanal‐Transistor ein Signal auf eine „saubere“ logische „0“ ziehen? Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 120 Auch die hier dargestellte Schaltung kann als Ausschnitt aus einer CMOS‐Schaltung interpretiert werden: • der P‐Kanal MOSFET wird als Pullup‐Transistor verwendet (Pullup‐Netzwerk), • Der Kondensator zwischen dem Ausgang und Masse repräsentiert die Summe aller am Ausgang angeschlossenen Gate‐Kapazitäten und Verdrahtungskapazitäten (jede Leitung hat auch eine kapazitive Wirkung zum Substrat der integrierten Schaltung und zu anderen Leitungen). Durch das Anschalten des Transistors ist die eigentliche Intention, die Ausgangsspannung uout auf UDD zu erhöhen und den Kondensator komplett aufzuladen. Ob dies gelingt, sollen Sie durch dieses Gedankenexperiment analysieren. Die Verwendung eines N‐Kanal‐MOSFETs im Pullup‐Netzwerk haben Sie bereits analysiert (vergleich vorletzte Folie) – hatte dies zufriedenstellend funktioniert? Anmerkung: Bei dieser Analyse spielt die Aufladezeit des Kondensators keine Rolle (Exponentialfunktionen), da die zeitliche Änderung von uG so langsam ist, dass die zeitliche exponentielle Änderung in dem hier verwendeten zeitlichen Maßstab nicht erkennbar sein wird. Dadurch, dass der P‐Kanal‐Transistor nur durchschaltet wenn uGS UTHp ist (UTHp < 0V), muss zunächst geklärt werden, ob der obere Transistor‐Anschluss in der Schaltung Drain oder Source ist. Da der obere Anschluss auf Versorgungsspannungspotential liegt – und dies das höchste (statische) Potential in der Schaltung ist – ist dies der Source‐Anschluss. Der untere Anschluss ist entsprechend der Drain‐Anschluss (die Anschlüsse sind in der Abbildung schon mit D und S beschriftet). Damit liegt der Source‐Anschluss auf dem festen UDD‐Potential !!! In der Aufgabenstellung ist nun die Gate‐Spannung (Gate gegenüber Masse) als Eingangssignal gegeben. Der Kondensator ist initial entladen (t = 0: C ist entladen, uout = 0V). Erst wenn der Transistor leitet, kann sich die Ausgangsspannung ändern – im Zeitintervall [0;t0) liegt die Gate‐Source‐Spannung uGS oberhalb der Schwellwertspannung UTH und damit sperrt der Transistor in diesem Zeitintervall. Der zeitliche Verlauf von uGS(blau) und uout(rot) sind im Zeitintervall [0;t0) bereits dargestellt und sollen von Ihnen für t>t0 nun ergänzt werden. Wie verhält sich der P‐Kanal MOSFET, wenn Sie nun versuchen, über einen P‐Kanal MOSFET im Pulldown‐ Netzwerk eine Kapazität zu entladen (vergleiche vorherige Folie – aber dieses Mal mit einem P‐Kanal MOSFET)? Fassen Sie Ihre Erkenntnisse über das „Durchschalten“ einer logischen „0“ und einer logischen „1“ durch einen N‐Kanal sowie P‐Kanal MOSFET abschließend zusammen. Anmerkung Folie: Eine logische „0“ wird als „sauber“ bezeichnet, wenn das Signal auf Massepotential liegt. Eine logische „1“ wird als „sauber“ bezeichnet, wenn das Signal auf Versorgungspotential (UDD) liegt. 120

Struktur CMOS‐Schaltungen Aus der Komplementarität von n‐Kanal und p‐Kanal‐ Transistoren ist es leicht verständlich, dass der p‐Kanal‐ Transistor keine gute logische „0“ erzeugen kann. Im pull‐up‐Block sind deshalb p‐Kanal‐Transistoren, im pull‐ down‐Block n‐Kanal‐Transistoren zu verwenden. Die p‐Kanal‐Transistoren des pull‐up‐Blocks erzeugen die logische „1“. Sie werden durch eine logische „0“ am Gate leitend. Die n‐Kanal‐Transistoren des pull‐down‐Blocks erzeugen die logische „0“. Sie werden durch eine logische „1“ am Gate leitend. CMOS‐Gatter sind meistens negierende Gatter, z. B. NOR, NAND, Inverter. Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 121 121

CMOS Inverter uGSp S uDSp UDD iDSp D iDSn D uIN uDSn uOUT uGSn S Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 122 Zur Analyse des elektrischen Verhaltens von CMOS‐Gattern wird der CMOS‐Inverter als Repräsentant verwendet. Das Pullup‐ und Pulldown‐Netzwerk könnte auch komplexer gestaltet werden (vergleiche z.B. NAND2‐Gatter) – das prinzipielle elektrische Verhalten wird dadurch aber nicht geändert. 122

Statische Übertragungskennlinie CMOS Inverter i DSp Sperrbereich: uGSp > UTHp; uDSp iDSp = 0 uGSp iDD S Sättigung Linearer uDSp uGSp Bereich UDD iDSp D uDSp=uGSp‐UTHp iDSn D uIN uDSn uOUT iDSn uDSn=uGSn‐UTHn uGSn S Linearer Bereich uGSn Sättigung uOUT=UDSn=UDD+UDSP uIN=UGSn=UDD+UGSp Sperrbereich: uGSn < UTHn; iDSn = 0 iDD=iDSn=‐iDSp uDSn 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 123 Ähnlich wie die Arbeitspunkte auf der Folie „Bipolar‐Transistor als Schalter“ aus der Transistor‐ Kennlinie des Bipolar‐Transistors und der Widerstandsgeraden ermittelt wurden, sollen hier die „statischen“ Arbeitspunkte aus den Transistorkennlinien ermittelt werden. Links ist hierzu der zu analysierende Inverter mit den relevanten Spannungen und Strömen unter Berücksichtigung der Transistor‐spezifischen Zählpfeilrichtungen dargestellt (in schwarzer Schrift). Die wesentlichen Spannungen und Ströme aus Gesamtgatter‐Sicht sind in grün beschriftet. Rechts sind die beiden Transistorkennlinien (oben P‐Kanal MOSFET, unten N‐Kanal‐ MOSFET) dargestellt. Zur Ermittlung der statischen Übertragungskennlinie (Uout=f(Uin)) werden die Darstellungen der Transistorkennlinien auf die Kenngrößen uin, uout und UDD transformiert: • uout=UDD+uDSp • iDD=‐iDSp • uin=UDD+uGSp • uout=uDSn • iDD=iDSn • uin=uGSn 123

Statische Übergangskennlinie CMOS Inverter ‐iDSp,iDSn,iDD uGSp uGSn uDSp uDSn Symetrische Übergangslinien wenn Widerstand von N‐ und P‐Kanal‐Transistor im leitenden Zustand gleich Wegen Faktor 2 ‐ 3 geringerer Beweglichkeit von Löchern (P‐ Kanal‐Transistor) gegenüber Elektronen muss W/L‐ Verhältnis vom P‐Kanal‐Transistor entsprechend um den Faktor 2 – 3 größer sein 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 124 124

Statische Übergangskennlinie CMOS Inverter ‐iDSp uGSp S uDSp uIN UDD iDSp D iDSn D uOUT uIN uDSn uOUT iDSn uGSn S uIN uOUT=UDSn=UDD+UDSP uIN=UGSn=UDD+UGSp iDD=iDSn=‐iDSp uOUT 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 125 125

Statische Übergangskennlinie CMOS Inverter iDD, uOUT iDD UDD uIN uIN Uinv uOUT Uinv UDD uIN UTHn UDD+UTHp uINUDD+UTHp: iDD0 und uOUT 0 uDSp UDD UTHn uIN UDD+UTHp : N‐ und P‐ iDSp D Kanal‐Transistoren leiten iDSn Logische Schwellwertspannung Uinv : D Uinv ist definiert als die Spannung, bei uIN uDSn uOUT der gilt: uIN = uOUT = Uinv uGSn S Uinv ~ UDD 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 126 Oben links sind die Kennlinien des p‐ und n‐Kanal MOSFETs in einem Diagramm dargestellt. Die jeweiligen Kennlinien mit der gleichen Eingangsspannung Uin sind in der gleichen Farbe dargestellt. Die Arbeitspunkte ergeben sich aus den Schnittpunkten der der gleichfarbigen Kennlinien. In der rechten Abbildung sind die daraus resultierenden Arbeitspunkte für idd und uout aufgetragen. In den Bereichen in denen eines der beiden Netzwerke (pullup oder pulldown) sperren, fließt kein nennenswerter Strom und die Ausgangsspannung entspricht entweder USS (Masse) oder UDD (Versorgungsspannung). Leiten beide Transistoren, fließt ein Querstrom durch den Inverter, der in bei uin=uout=unv seinen Maximalwert erreicht. In dem mittleren Bereich der Spannungsübertragungskurve (rechte Abbildung, zwischen dem roten und lilafarbenen Punkt) führen kleine Änderungen an der Eingangsspannung uin zu großen Spannungsänderungen am Ausgang (uout). Wenn in diesem Arbeitsbereich die Eingangsspannung durch Störungen verändert wird, so hat dies entsprechend große Auswirkungen am Ausgang – und entsprechend sollte der Transistor im stabilen Zustand nicht in diese Arbeitsbereiche gelangen (insbesondere nicht durch Störungen – z.B. kapazitive Leitungskopplungen). Dies spielt eine große Rolle bei der Wahl der Spannungsbereiche, die für den logischen 0‐ und logischen 1‐ Pegel verwendet werden. Außerdem wird dadurch der Störspannungsabstand definiert (siehe folgende Folien). Ein wichtiger Punkt ist unten rechts in der Folie in rot dargestellt: Uinv ~ UDD Die logische Schwellwertspannung ist näherungsweise direkt proportionale zur Versorgungsspannung (in der Praxis im Bereich von 50%∙UDD). D.h. – anders als bei TTL‐ Techniken – können CMOS‐Schaltungen mit unterschiedlichen Versorgungsspannungen betrieben werden. Die Grenzen sind primär dadurch definiert, dass die Isolationsschichten oder die sperrenden Soruce‐Drain‐Übergänge bei zu hohen Spannungen per Lawineneffekt durchschlagen und damit der Transistor nicht mehr funktionstüchtig ist und sogar geschädigt werden kann. 126

Störspannungsabstand 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 127 SSAH und SSAL sind Störspannungsabstände (engl.: noise margin) und geben die maximale Spannungsschwankung an, durch die das logische Ausgangs‐Signal nicht verändert wird. Die Spannungswerte am Ausgang bzw. Eingang einer Schaltung unterliegen Technologie‐ und Temperaturschwankungen. Sie können durch äußere Störungen, z.B. Strahlung oder Übersprechen (bei parallel liegenden Leitungen können elektrische Felder dazu führen, dass Impulse von der einen auf eine andere Leitung "überspringen") verändert werden. Bei zu großen Störungen treten logische Fehler auf, bleibt die Störung jedoch im Bereich der Störspannungsabstände, so wird die Störung gedämpft. Der Störspannungsabstand wird hier untersucht für die Serienschaltung zweier Inverter. Der Übergang von einem definierten zu einem undefinierten Wert ist dort, wo eine differentiell kleine Änderung der Eingangs‐Spannung eine große Änderung der Ausgangs‐Spannung bewirkt. Also dort, wo die Steigung der Ein‐Ausgabe Kennlinie 1 bzw. ‐1 ist. Diese Übergänge sind im Diagramm durch die Punkte C und D markiert. Am Ausgang eines Gatters ist VOHmin der minimale Wert für eine logische 1. Ein direkt nachfolgendes Gatter erkennt eine logische 1 sogar noch korrekt, wenn der Eingangspegel größer oder gleich VIHmin ist. Das maximale Störsignal darf also SSAH sein: SSAH=|VOHmin‐VIHmin| Entsprechend wird der Ausgang eines Gatters bis maximal VOLmax als logische Null interpretiert. Das nachfolgende Gatter erkennt einen Spannungspegel von maximal VILmax noch als logische 0. Also: SSAL=|VILmax‐VOLmax| Das Diagramm des zweiten Inverters kommt durch Spiegelung an der Winkelhalbierenden zustande. Damit die Störspannungsabstände SSAH und SSAL annähernd gleich groß sein können, sollte die logische Schaltschwelle Vinv =UDD/2 sein. 127

Body‐Effekt Bei Serienschaltung von MOS Transistoren ist der Source‐Anschluss ggf. nicht auf dem Potential des Substrats. Zwei Effekte treten auf: Body‐Effekt, eine betragsmäßige Vergrößerung der Schwellwertspannung UTH: U TH U TH 0 U S mit γ 0,5 ; US = Source‐Potential Die Gate‐Source Spannung von T1 ist wegen des Spannungsabfalls über T2 kleiner als UG, deshalb wird der Drainstrom zusätzlich begrenzt. 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 128 Bei MOS‐Schaltungen sind alle Transistoren auf dem selben Substrat (Bulk) angeordnet. Normalerweise ist daher das Substrat‐Potential überall gleich dem Masse‐Potential und die Source‐Substrat‐Spannung USB=0. Durch Anordnen mehrerer Transistoren in Reihe steigt das Source‐Potential und damit die Source‐Substrat‐Spannung bei nachgeschalteten Transistoren an. Für diese Transistoren ist USB>0. Das bewirkt ein Ansteigen der Schwellwertspannung UTH und daher kleinere Kanalströme. 128

Modellbildung in CMOS‐Schaltungen Ziele: Verständnis erstes einfaches Verzögerungszeitmodell für integrierte CMOS‐Schaltungen Verständnis wodurch in CMOS‐Schaltungen Verzögerungen zustande kommen Verständnis wie sich die Verzögerungszeiten bei der Verkleinerung von Transistoren ändert („shrinking“) Verständnis wodurch in CMOS‐Schaltungen Verlustleistung in Wärme umgesetzt wird Verständnis wie sich die Verlustleistung bei der Verkleinerung von Transistoren ändert („shrinking“) 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 129 129

Verzögerungszeit: Einfaches Switch‐Level Modell ≈ RK CG Der Kanalwiderstand eines Transistors kann näherungsweise als Widerstand mit dem Widerstand RK modelliert werden (Charakteristikum des treibenden Gatters). Der Eingang eines Transistors kann näherungsweise als Kondensator mit der Kapazität CG modelliert werden (Charakteristikum des getriebenen Gatters). Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 130 Repräsentativ für eine Verschaltung von Logikgattern wird hier die Serienschaltung von zwei Invertern betrachtet. Ähnlich wie bei den statischen Kennlinien hätten hier auch beliebige andere Pullup‐ und Pulldown‐Netzwerke analysiert werden können. Die Erkenntnisse werden dadurch aber nicht anders sein – und deshalb: „Let‘s keep it simple!“ 130

Switch‐Level Modell: CMOS‐Gatterstufen Aus dem einfachen Transistormodell folgt, dass beim Umschalten eines Gatterausgangs zwischen „0“ und „1“ eine Kapazität, die resultierende Kapazität CL der getriebenen Folgegatter und der Leistungskapazitäten, über dem resultierenden Kanalwiderstand RK der pull‐up‐Transistoren des treibenden Gatters aufgeladen werden muss. ur RK i t0 UDD CL uC=0 | t

Ladevorgang am Kondensator dQ dCuC du i CL C dt dt dt RK i t0 u R i RK UDD CL uC=0 | t t0 u R uC U DD 0 uC UDD uR UDD i RK d (U DD iRK ) di i CL RK CL dt dt Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 132 Die Lösung der Differentialgleichung zur Ladung des Kondensators ist hier zur Vollständigkeit und Wiederholung dargestellt. Dies ist aber nicht primärer Bestandteil dieser Vorlesung… 132

Lösung der Differentialgleichung di allgemeiner Ansatz: i a b e ct i RK C L dt t ; i 0 a 0, c 0 t 0; u C 0 u R U DD i0 R K Das Bildelement mit der Beziehungs-ID rId20 wurde in der Datei nicht gefunden. i i0 e ct i R K C L i0 ce ct di i0 c e ct t = 0, i = i0 dt 1 i R K C L i0 c c t RK C L R K C L i i0 e Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 13.05.2021 – Prof. Dr.‐Ing. Wolfgang Nebel – Univ. Oldenburg 133 Die Lösung der Differentialgleichung zur Ladung des Kondensators ist hier zur Vollständigkeit und Wiederholung dargestellt. Dies ist aber nicht primärer Bestandteil dieser Vorlesung… 133

Verzögerungszeit t U DD i i0 e RK C L i0 RK RK t i t0 uC U DD RK i U DD (1 e RK CL ) UDD CL uC=0 | t

Verzögerungszeit: Switch‐Level Modell Steigende (01) und fallende (10) Ausgangsflanke Hier: steigende Ausgangsflanke P‐Kanal‐Transistor mit effektivem Kanalwiderstand RK beginnt zum Zeitpunkt t0 zu leiten (also Uin=UDD|t

Verzögerungszeit: Switch‐Level Modell Hier: fallende Ausgangsflanke Unterschied steigende Flanke: effektiver Kanalwiderstand vom N‐Kanal‐Transistor N‐Kanal‐Transistor mit effektivem Kanalwiderstand RK beginnt zum Zeitpunkt t0 zu leiten (also Uin=USS|t

Verzögerungszeiten ‐ Einflußfaktoren Einflußfaktoren Verzögerungszeiten von CMOS‐ Gatterstufen: Zuordnung der Einflußfaktoren: Treiber‐Gatterstufe (DRV = Driver) kapazitive Last (Load) Stimulus: sämtliche Gatter‐Eingangssignale z.B. Komplexgatter Z A ( B C,)Verzögerungszeit fallende Flanke AZ 3 Möglichkeiten für Signalpegel B,C: Z RK A B C Z RA RA+RC 0 1 RK(Pulldown) RA+RB 1 0 RB RC RA+(RB||RC) 1 1 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 137 137

Verzögerungszeiten ‐ Einflussfaktoren Primäre Einflußfaktoren auf Verzögerungszeiten von CMOS‐ Gatterstufen (grobe Wichtung der Relevanz von ! bis !!!!): RK: Effektiver Kanalwiderstand: Weite/Länge‐Verhältnis der am Schaltvorgang beteiligten Transistoren (DRV) (!!!!) ggf. Zustand weiterer Transistoren: welche Serientransistoren im jeweiligen Pullup‐ bzw. Pulldown‐Netzwerk leiten (DRV, Stim) (!!) Widerstand Verdrahtung (! – bei kleinen Strukturgr. zunehmende Bedeutung) CL: Lastkapazität: Summe Gate‐Kapazitäten angeschlossener MOS‐Transistoren (Load) (!!!!) Kapazität Verdrahtung (Load) (!!!!) gatterinterne kapazitive Effekte: z.B. Drain‐Kapazitäten sperrender Transistoren (DRV) (!!) Signalform des Eingangssignals, das zum Schalten des Gatters führt (Kenngröße Flankensteilheit) (!!) 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 138 138

Verzögerungszeiten ‐ Einflußfaktoren Sekundäre Einflussfaktoren (d.h. Beeinflussung der primären Einflussfaktoren) auf Verzögerungszeiten von CMOS‐Gatterstufen: Betriebsspannung UDD (beeinflusst primär RK, Uinv) Temperatur (beeinflusst primär RK) Variationen des Herstellungsprozesses (beeinflusst RK und CL) 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 139 139

Verzögerungszeiten ‐ Einflussfaktoren Weitere Effekte, die nicht weiter betrachtet werden: Gleichzeitige Eingangssignaländerungen Kanalwiderstand hängt von der Drain‐Source‐Spannung ab und ist damit nicht konstant während der Signaländerung am Gatterausgang Leitwert sinkt mit steigender iDSn Ausgangsspannung (Steigungsdreieck) Sättigung uGSn Linearer Bereich u u uDSn 13.05.2021 t t Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 140 140

Verlustleistung Betrachteter Signalwechsel am 2. Gatter: eine steigende und eine fallende Flanke (Bild nur steigende Flanke) CL wird 1x auf‐ und 1x entladen. Energie wird in RK in Wärme umgesetzt: · Verlustleistung bei Schaltfrequenz f: P · · RK i t0 UDD CL RK C uC=0 | t

MOS Transistor – shrinking (mehr Transistoren pro Fläche) x=0 x=L x Al SiO 2 W Gate "G" n p n d Drain "D" Kanal Source "S" Si Substrat "B" G Alle Abmessungen (W, L, d) und die Versorgungsspannung werden proportional um den Faktor 1/S skaliert (S>1). D S W. Nebel; Technische Informatik – Universität Oldenburg 13.05.2021 D. Rabe; HS Emden/Leer 142 Primär schon aus wirtschaftlichen Gründen werden die minimalen Abmessungen von einem Transistoren stetig gesenkt. Die Abmessungen werden aktuell bereits in Nanometern angegeben. Die Grenzen für die minimalen Abmessungen sind technologische Herausforderungen bei der Herstellung der integrierten Schaltungen. Im Folgenden soll nun die Auswirkung der Verzögerungszeit auf die Schaltzeiten und die Verlustleistung analysiert werden. 142

Auswirkungen der Transistorskalierung Parameter Skalierungsfaktor · Gatekapazität ⁄ ⁄ Elektrisches Feld ~ 1 (konstant!) ⁄ ⁄ Kanal‐Widerstand (leitend): ~ 1 ⁄ Verzögerungszeit ~ · 1· Verlustleistung pro Transistor: · · ⁄ · · ~ · · Anzahl Transistoren pro integrierte Schaltung: _ ~ Verlustleistung pro integrierte Schaltung (konst. Chipfläche): · · _ Verlustleistung pro integrierte Schaltung (Skalierung Chipkante um ): · _ 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 143 Der primäre Motor für die „ständige“ Verkleinerung von Transistor („Shrinking“) sind wirtschaftliche Aspekte (geringer Chipfläche ‐> Kosteneinsparung; mehr Funktionalität pro Chip). In der Realität werden die eingesparten Flächen bei neuen Produkten für zusätzliche Funktionen / Speichergrößen usw. verwendet. D.h., die Chips werden nicht kleiner aber leistungsfähiger. In der Realität werden sie oft sogar größer (siehe Shrinkfaktor SC). Die Größe eines Chips wird dadurch begrenzt, dass bei der Herstellung auch Defekte auftreten. Je größer der Chip ist, desdo größer ist die Wahrscheinlichkeit, dass ein Chip nicht fehlerfrei funktioniert aufgrund eines solchen Defekts (siehe auch folgende Folien zur Ausbeute). Auch dies sind wieder wirtschaftliche Aspekte. Die positiven Auswirkungen auf die Verzögerungszeit sind ebenfalls wichtig – aber eher in zweiter Linie. Bezeichner: CG: Gatekapazität; A: „Kondensator“fläche (Kondensator‐Elektroden sind Gate und Kanal); d: Oxid‐Dicke (Dicke des Kondensators); W: Weite des Transistors (Breite); L: Länge des Transistors; RK: effektiver Kanalwiderstand im eingeschalteten Zustand; : Verzögerungszeit; PTr: Verlustleistung pro Transistor; f: Schaltfrequenz des Transistors (ist umgekehrt proportional zur Verzögerungszeit ); nTr_Chip: Anzahl Transistoren pro Chip (durch Shrink mehr Transistoren pro Chip integrierbar); PChip: Verlustleistung pro Chip Sinkende horizontale Abmessungen führen zu kleineren Knotenlängen und Weiten der Kanäle Die Gatekapazität ist näherungsweise proportional zur Gatefläche und umgekehrt proportional zur Oxid‐Dicke d Die Gatekapazitäten sinken linear mit kleineren Feature Sizes. Der Kanalwiderstand ist proportional zum Länge/Breite Verhältnis der Kanäle (L/W bleibt konstant): Auch wenn dies eine vereinfachte Sichtweise ist (eigentlich sollte der Quotient analysiert werden), so stimmt das Ergebnis dennoch In Summe: CL sinkt etwa linear mit Feature Size RK ist etwa konstant τ sinkt, fCIK steigt linear PChip bleibt in etwas konstant (typischerweise steigt aber auch noch die Chipfläche und damit die Verlustleistung) Die Einbeziehung der Verdrahtungskapaziäten in die Lastkapazitätsberechnung und der Verdrahtungswiderstände ändert die dargestellten Proportionalitäten nicht wesentlich (siehe z.B. Dissertation Rabe – „Accurate Power Analysis of Integrated CMOS Circuits on Gate Level” ‐ http://oops.uni‐ oldenburg.de/341/ , S.9‐19) Durch die steigende Chip‐Flächen und oftmals nicht ganz linear ge‐shrinkte Versorgungsspannungen steigt die Verlustleistung von integrierten Schaltungen zunehmend an – und die Wärme muss abgeführt werden (Lüfter…) 143

Ausbeute (probe yield) wafer Fehler die Die Ausbeute Y, auch Fertigungsausbeute oder Meßausbeute genannt, ist der Anteil funktionsfähiger ICs (engl. dies) aller gefertigten ICs eines Wafers funktionsfähige ICs Y= gefertigte ICs Beispiel: klein: 138 gute von 156 ICs Y 88% groß: 18 gute von 32 ICs Y 56% Flächenfaktor: 4 Ausbeutefaktor: ≈ 8 (138/18) W. Nebel; Technische Informatik – Universität Oldenburg 13.05.2021 D. Rabe; HS Emden/Leer 144 Chips (oder "dies" ) werden nie einzeln, sondern zu mehreren auf einem Wafer hergestellt. Bei gleichbleibender Chipgröße kann auf großen Wafern mehr Waferfläche für Chips genutzt werden, da die ungenutzte Randflächen der runden Wafer im Verhältnis zur genutzten Fläche kleiner wird. Außerdem können auf großen Wafern pro Arbeitsschritt mehr "dies" hergestellt werden. Früher waren Wafer 4 oder 5 Zoll groß, heute sind 8 Zoll üblich. Fehlerhafte "dies" verringern die Ausbeute. Fehler entstehen durch Kristallfehler im Silizium und durch Verunreinigungen von Maske und Material. Im Beispiel soll die IC‐Größe ein kleines Quadrat betragen. Dann erhält man aus dem abgebildeten Wafer von insgesamt 156 möglichen 138 funktionsfähige ICs. Vervierfacht man die Chipfläche, indem man die großen Quadrate als einen Chip auffaßt, so erhält man nur noch 18 gute von 32 möglichen ICs. Beim Vergrößern der Chipfläche um den Faktor 4 sinkt also die Ausbeute um den Faktor 1/8. 144

Minimum Feature Size und Ausbeute Wirtschaftliche Abwägung: kleine min. feature size ‐> kleinere Chipfläche; einfaches Ausbeutemodell: kleinere Chipfläche ‐> -DA mehr dies pro Wafer; kleinere Chipfläche ‐> Y=ce bessere Ausbeute (yield) mit: D : Defektdichte aber: A : IC‐Fläche kleinere min. feature size ‐> höhere Problem: Fehleranfälligkeit wird Fehleranfälligkeit; bei diesem Modell nicht abhängig höhere Fehleranfälligkeit von der minimum feature size ‐> geringere Ausbeute. berücksichtigt! gesucht: Optimum! W. Nebel; Technische Informatik – Universität Oldenburg 13.05.2021 D. Rabe; HS Emden/Leer 145 145

Vergleich TTL CMOS Vorteile CMOS gegenüber TTL: Höhere Integrationsdichte (LargeScaleIntegration – LSI, VLSI (v=very), ULSI (u=ultra), …, GLSI (g=giant)) Bei kleiner Betriebsfrequenz geringere Verlustleistung (näherungsweise keine statischen Ströme, bei TTL stromgesteuerte Transistoren) Im statischen Fall keine Eingangsströme (nur bei Pegel‐ Wechsel durch kapazitive Auf‐ und Endladung, bei TTL statische Ströme bei Low‐Pegeln) Pegelmäßig höhere Störsicherheit bei CMOS‐Schaltungen Bei CMOS: Schaltschwellen (Ausgang mit Eingang verbinden) relativ zur Versorgungsspannung, bei TTL nicht Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 146 Abkürzung Bezeichnung Komplexität (Gatteräquivalente) Typische Interpretation SSI small scale integration 10 MSI medium scale integration 100 LSI large scale integration 1.000 VLSI very large scale integration 10.000–100.000 ULSI ultra large scale integration 100.000–1.000.000 SLSI super large scale integration 1.000.000–10.000.000 ELSI extra large scale integration 10.000.000–100.000.000 GLSI giant large scale integration > 100.000.000 1 Gatteräquivalent = 1 NAND2‐Gatter normaler Treiberstärke = 4 Transistoren Quellen: • https://de.wikipedia.org/wiki/Integrationsgrad • https://en.wikipedia.org/wiki/Gate_equivalent 146

Vergleich TTL CMOS Vorteile TTL gegenüber CMOS: CMOS: Empfindlich gegenüber elektrostatische Aufladung (siehe Folien zum Thema ESD‐Schutz) CMOS: Hochohmigere Schaltungen => höhere Störempfindlichkeit Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 147 147

Historisch: NMOS‐Technologie NMOS: keine P‐Kanal‐Transistoren Pull‐Up‐Netzwerk wird durch einen selbstleitenden N‐Kanal‐ Transistor ersetzt: UTHn_selbstleitend < 0V separater Fertigungsschritt für selbstleitende Transistoren erforderlich NMOS‐Technologie hat heute keine Bedeutung mehr hier nur eingeführt, um Charakteristiken der CMOS‐Technologie vergleichend diskutieren zu können 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 148 148

Vergleich NMOS und CMOS Technologie CMOS NMOS Logikpegel 1: UDD 1: UDD 0: USS 0: 0,2 UDD (Pullup‐ Netzwerk immer leitend) Schwellwert UINV / Versor‐ Prozentsatz von UDD / max. Abhängig von UDD / festes gungsspannungsbereich UDD technologieabhängig UDD (Oxid‐Durchschlag) Verlustleistung Nur beim Schalten (von Beim Schalten und bei Subthreshold‐Strömen logischem 0‐Pegel abgesehen) Packungsdichte 2N Transistoren pro Gatter‐ N+1 Transistoren pro stufe (N Anzahl der Gatterstufe Eingänge) 13.05.2021 Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 149 149

4. Lernzielmatrix „MOSFETs und CMOS‐Gatter“ ‐ I a. Kennen b. Können c. Verstehen und Anwenden 1. Fachlich • Angeben von statischen und • Untersuchen die • Analysieren die dynamischen (P/N‐)MOSFET‐ Funktion von elektrischen Charakteristiken, des physikalischen komplementären Charakteristiken von Aufbaus und der MOSFET‐Symbole Logikgattern Schaltungsanordnungen • Angeben der für CMOS‐Gatter (mit mit NMOSFETs und charakteristischen elektrischen Schaltern/MOSFETs) PMOSFETs („sauberes“ Eigenschaften (statische Durchschalten von Übergangskennlinien, logischen „0“‐ und „1“‐ Störspannungsabstand, Pegeln) Verzögerungszeiten, Verlustleistung MOS‐Transistor‐Effekte) Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 150 Die in grün dargestellten Themen sind nur für die Veranstaltung Digitaltechnik (4+2) und nicht für die Veranstaltung „Digitaltechnik für Informatik“ (3+1) die Lernziele. 150

4. Lernzielmatrix „MOSFETs und CMOS‐Gatter“ ‐ II a. Kennen b. Können c. Verstehen und Anwenden 2. Methodisch • Untersuchen die elektrischen • Beurteilen die Vor‐ und Nachteile der Eigenschaften von CMOS‐ CMOS‐Technologie gegenüber anderen / überfachlich Schaltungen mit dem Technologien Switch‐Level‐Model • Beurteilen die Auswirkungen des (Schalter, Widerstände, „Shrinkings“ auf elektrische und Kapazitäten) wirtschaftliche Auswirkungen und ziehen daraus Schlussfolgerungen für die Halbleiterentwicklung 3. Sozial • Artikulieren der unterschiedlichen Charakteristiken der CMOS‐ Technologie gegenüber anderen Technologien (TTL, NMOS, …) 4. Persönlich • Übernehmen Verantwortung für eigenes Lernen und hinterfragen eigenes Verständnis Digitaltechnik – Prof. Dr.‐Ing. Dirk Rabe – HS Emden/Leer 151 Die in grün dargestellten Themen sind nur für die Veranstaltung Digitaltechnik (4+2) und nicht für die Veranstaltung „Digitaltechnik für Informatik“ (3+1) die Lernziele. 151

Sie können auch lesen